一颗晶振能为多个芯片同时提供参考时钟信号吗?

举例:在某款控制主板上有CPU、CPLD、网络处理ASIC、时钟发生器等多颗芯片,都需要25MHz的参考时钟信号,可以选择的方案有:

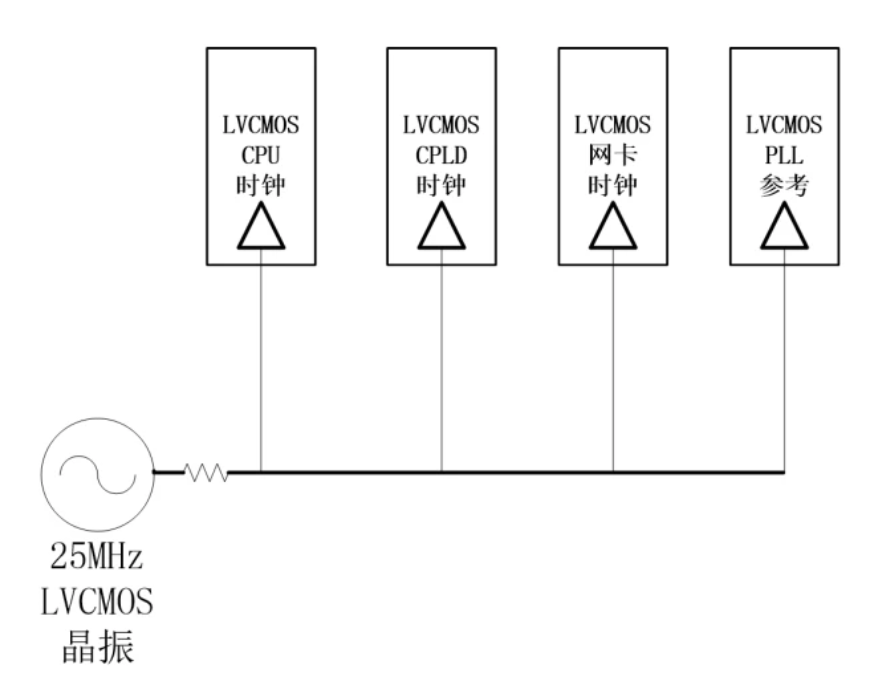

方案1:

选择一颗晶振同时为几个芯片提供参考,这种方案很大的弊端是时钟信号完整性问题(如产常规有源晶振的负载为15pF,一般情况下可以负载1~2个芯片;如果负载3~4芯片,建议选择负载为30pF或50pF的有源晶振)。这种点到多点的连接无法做到阻抗匹配,信号反射会很严重,导致时钟信号沿的单调性、过冲振铃等问题,进而可能导致误触发,造成系统失步,因此多数应用都需要点对点的拓扑。如下图所示:

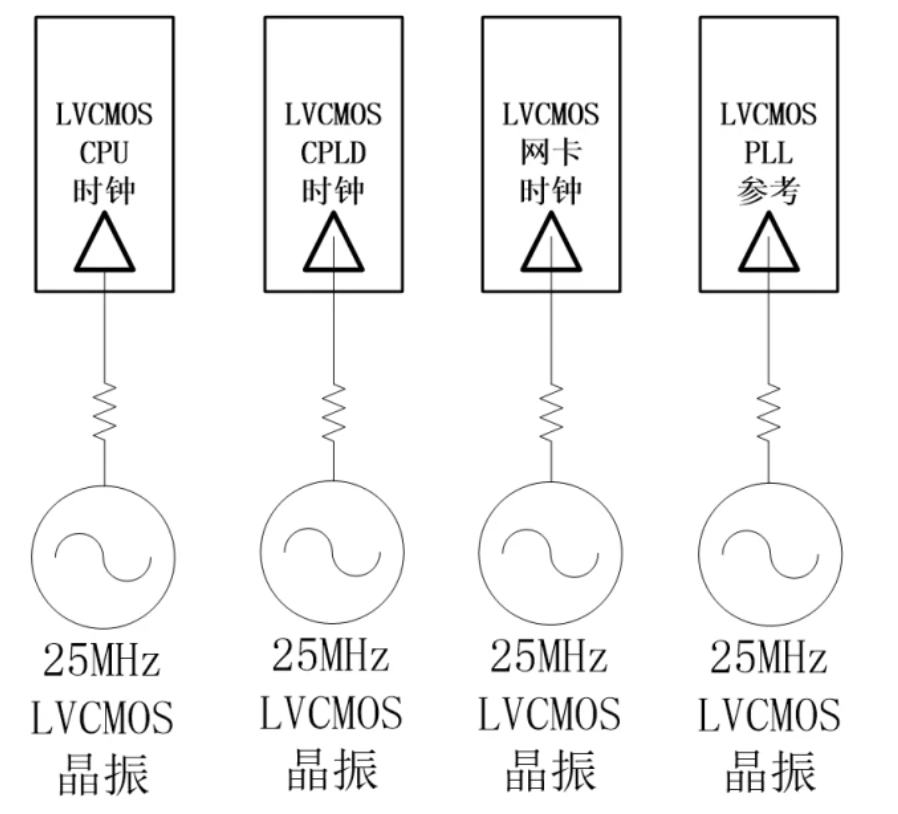

方案2:

选择4颗晶振分别给4个芯片提供参考,这个方案的优势就是PCB布局走线更灵活方便,可以保证时钟信号的完整性。当然明显的劣势就是成本高,特别是对于参考频率指标要求高的场景,高性能的晶振本身成本就高,往往功耗也比较高,电源部分的处理会进一步增加方案成本。另外布局灵活的同时,也会占用更大的PCB板空间。如下图所示:

方案3:

一颗晶振加上一个时钟缓冲器(Buffer)芯片,这也是最常用的方案。通过Buffer的频率复制功能,可以做到点到点的拓扑结构,很好的解决信号完整性问题,做到最佳性价比。如下图所示: