寄生的含义就是本来没有在那个地方设计电容,但由于布线之间总是有互容,互容就好像是寄生在布线之间的一样,所以叫寄生电容,又称杂散电容。

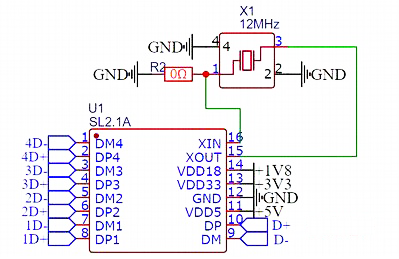

寄生电容本身不是电容,根据电容的原理我们可以知道,电容是由两个极板和绝缘介质构成的,那么寄生电容是无法避免的。比如一个电路有很多电线,电线与电线之间形成的电容叫做寄生电容。寄生电容一般在高频电路(晶振时钟信号)中会对电路造成很大影响,所以电路在布线的时候要特殊考虑。

寄生电容一般是指电感,电阻,芯片引脚等在高频情况下表现出来的电容特性。实际上,一个电阻等效于一个电容,一个电感,和一个电阻的串连,在低频情况下表现不是很明显,而在高频情况下,等效值会增大,不能忽略。在计算中我们要考虑进去。ESL就是等效电感,ESR就是等效电阻。不管是电阻,电容,电感,还是二极管,三极管,MOS管,还有IC,在高频的情况下我们都要考虑到它们的等效电容值,电感值。

针对杂散电容,寄生电容,分布电容这三个说法,有人认为这三个说法区别不大,只是适用场景不同,针对器件时多用“寄生电容”,针对系统时多用“分布电容”。但是,若更加严谨一点的话,这三者还是存在一些细微区别的,解释如下:

寄生电容

在现代工艺水平下,生产器件的某个功能时所不可避免地产生的另一种现象,比如现代生产二极管的时候,由于工艺限制无法制作出理想二极管,生产时不可避免的产生了电容。

分布电容

一般不是针对单个器件的,多数是讲在电路中产生的附加电容,例如电路中两个器件,它们肯定会有电容存在;同理,两条平行的输电线路间肯定也会有电容存在。

杂散电容

除以上两种电容外的其它形式的电容,例如两个器件、导体相互感应所产生的电容等。

杂散电容,寄生电容,分布电容的电容值可能极小,但是在特高频、超高频等情况下有时候还是不能忽略的,如晶振输出的时钟信号。如果PCB寄生电容很大的话,会直接影响到无源晶振输出频率的精度和稳定度。严重的话,可能会造成晶振时振时不振。杂散电容理论上无法消除,只能尽可能减小其对晶振时钟信号的干扰性。

杂散电容的影响

1、杂散电容会改变晶振的负载,从而影响其频率输出。晶振的输出频率与其负载电容密切相关,而杂散电容的存在相当于增加了额外的负载,导致晶振的实际输出频率偏离设计值。

2、杂散电容会导致电路中的能量损失增加,降低晶振的稳定性和可靠性。在高频电路中,杂散电容的存在会使得电路中的信号衰减加剧,从而影响晶振的振荡稳定性。

3、杂散电容还可能引起电路中的谐波干扰,进一步影响系统的性能。谐波干扰会破坏信号的完整性,导致数据传输错误或系统性能下降。

如何减少杂散电容?

1、选择具有低介电常数的材料作为电路板材料,可以降低杂散电容的影响。

2、提高电路板的绝缘性能也可以有效减少杂散电容的产生。

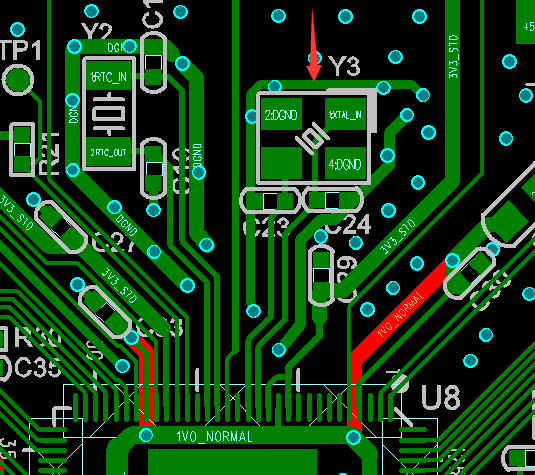

3、在电路板布局和走线时,需要考虑到晶振的位置和连接方式。

4、合理布局和走线可以减小晶振与其他元件之间的耦合电容,从而降低杂散电容的影响。

5、对于高频信号线,需要尽量减小其长度和弯曲程度,以减少信号失真和干扰。

6、在晶振附近增加去耦电容可以有效地减小电源和地线上的噪声,从而降低杂散电容的影响。去耦电容的选择需要根据具体的电路情况进行确定。

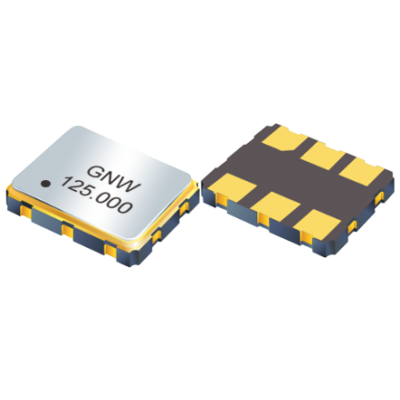

7、提高元件的装配精度可以减小元件之间的距离和偏差,从而降低杂散电容的产生。

8、采用具有高稳定性的元件也可以提高整个系统的性能。

拓展阅读:关于环境因素对晶振稳定性及寿命造成的影响

1、电压

电压是影响晶振寿命的重要因素之一。晶振的工作电压有其额定值,超过这个值就会对晶振造成过度的压力,导致其寿命降低。此外,电压的波动也会对晶振产生影响。电压波动可能导致晶振的频率发生偏移,从而影响其稳定性。因此,在使用晶振时,应确保其工作电压在额定范围内,并尽量减少电压波动。

2、温度

温度对晶振的影响主要体现在其频率稳定性上。晶体的振动频率会随着温度的变化而变化。在设计和使用晶振时,应充分考虑温度对晶振的影响,通过温度补偿措施,保证晶振在不同的温度下都能保持稳定的频率输出。

3、湿度

湿度对晶振的影响主要体现在湿度变化导致的晶体表面污染和腐蚀。湿度较高时,空气中的水分容易侵入晶振的封装材料,导致晶体表面产生氧化层,影响其振动性能。因此,在使用晶振时,应确保其工作环境干燥,避免高湿度对晶振的影响。